关于一种完全自对准导孔的半镶嵌工艺

作者:网站管理员

来源:本站原创

日期:2023/1/21 11:45:39

点击:8826

属于:技术资讯

在逻辑半导体多层布线工程(BEOL)中,取代以往的双镶嵌(Dual damascene),半镶嵌(Semi-damascene)可以将互连工艺流程发展至20nm以下的金属间距,且效费比高。在半导体器件的制造过程中,在绝缘膜上形成布线沟槽和导孔(连接上下布线的布线沟槽)后,沉积布线金属材料,同时填充二者,通过研磨使沟槽内仅留下布线金属从而形成多层布线的方法。它区别于单镶嵌(Single damascene)那种线路和导孔分别形成的方式。 例如铜这样难以刻蚀的金属也可以用作布线材料。由于布线金属被研磨,因此无需层间的平坦化工序即可获得平坦的布线结构,具有微细布线的多层化更加容易、减少制造工序数、降低制造成本的优点。 特别是在0.18μm规则之后的逻辑器件中,为了改善布线延迟采用的铜的双镶嵌布线方式大致可分为两种:先形成布线凹槽后再形成导孔(trench first)、先形成导孔后再形成布线凹槽(via first)。

在逻辑半导体多层布线工程(BEOL)中,取代以往的双镶嵌(Dual damascene),半镶嵌(Semi-damascene)可以将互连工艺流程发展至20nm以下的金属间距,且效费比高。在半导体器件的制造过程中,在绝缘膜上形成布线沟槽和导孔(连接上下布线的布线沟槽)后,沉积布线金属材料,同时填充二者,通过研磨使沟槽内仅留下布线金属从而形成多层布线的方法。它区别于单镶嵌(Single damascene)那种线路和导孔分别形成的方式。 例如铜这样难以刻蚀的金属也可以用作布线材料。由于布线金属被研磨,因此无需层间的平坦化工序即可获得平坦的布线结构,具有微细布线的多层化更加容易、减少制造工序数、降低制造成本的优点。 特别是在0.18μm规则之后的逻辑器件中,为了改善布线延迟采用的铜的双镶嵌布线方式大致可分为两种:先形成布线凹槽后再形成导孔(trench first)、先形成导孔后再形成布线凹槽(via first)。

imec(微电子研究中心)在2022年超大规模集成工艺与电路大会IEEE VLSI Symposium on Technology and Circuits (VLSI 2022)上发表了如下标题的全球首次实验性的18nm金属间距的2层金属层级的半镶嵌(Semi-damascene)演示。

《First demonstration of two metal level semi-damascene interconnects with fully self-aligned vias at 18MP'》

即Interuniversity Microelectronics Centre成立于1984年,目前是欧洲领先的独立研究中心,研究方向主要集中在微电子,纳米技术,辅助设计方法,以及信息通讯系统技术(ICT). IMEC 致力于集成信息通讯系统设计;硅加工工艺;硅制程技术和元件整合;纳米技术,微系统,元件及封装;太阳能电池;以及微电子领域的高级培训。IMEC总部设在比利时鲁汶(Leuven, Belgium),雇员超过一千七百名,包括超过三百五十名常驻研究员及客座研究员。IMEC有一条0.13微米8寸试生产线并已通过ISO9001认证。IMEC年收入超过一亿两千万欧元,均来自于其他合作者的授权协议及合约,包括比利时佛兰芒(Flemish)当地政府及公司、欧共体、MEDEA+、欧洲航天局、设备原材料厂商、以及世界各地的半导体和系统厂商。

该论文的作者imec BEOL研发团队的骨干研究员Gayle Murdoch和imec的纳米互连项目总监Zsolt Tokei对此项技术的解说,强调了在狭小间距下导孔自对准(self-alignment)的重要性,并以一种易于理解的方式解释了模块的关键技术参数(导孔和线路的电阻值、可靠性等)。

在这20多年中,Cu双镶嵌一直是制作高可靠性互连的主力工艺流程。但是,随着尺寸的缩放(比例缩小),金属间距缩至20nm以下,BEOL(Back End Of Line:布线工程)中的RC延迟日益严重。这迫使从事互连(interconnect)研究的人开始寻找金属间距小且具备优异性能指数的互连方案及金属材料替代品。

大约5年前imec率先提出,在1nm(及今后更小的)技术节点中最重要的局部(Mx:x对应的是从下往上所占第几层的层数)相互连接层的形成工艺方面,“半镶嵌”可作为Cu双镶嵌的可行的替代方案。

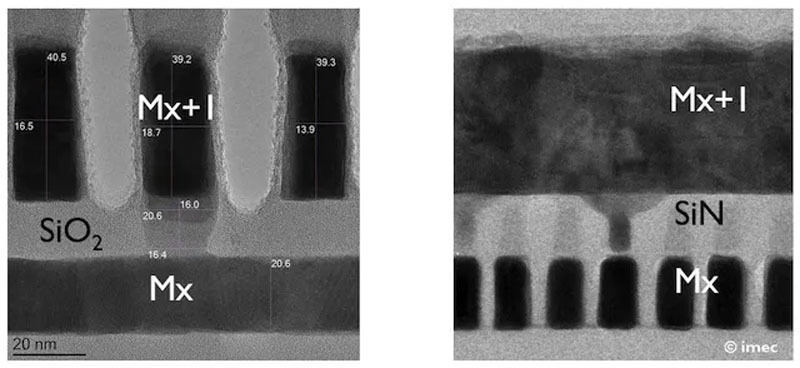

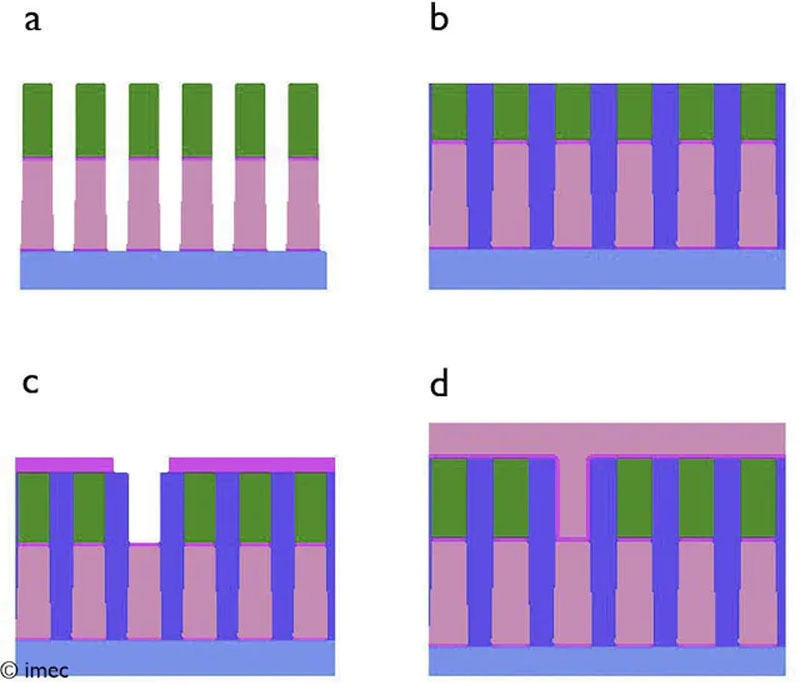

图1:imec的半镶嵌工艺流程。(a)Ru刻蚀(底部局部互连线(Mx)的形成)、(b)填充缝隙、(c)孔的刻蚀、(d)向孔内埋入金属和顶线(Mx+1) (出处:imec,以下皆是。)

与双镶嵌不同的是,半镶嵌式堆积依靠互连金属的直接图案化(被称为缩减金属化),不需要对金属进行化学机械抛光(CMP)来完成布线工程。后续连接互连层的孔会以单镶嵌方式进行图案化,接着会被填充过量的金属。也就是说层间绝缘膜电介质上会不断沉积金属直至形成金属层。然后,对这个金属层进行覆膜,刻蚀,形成拥有正交线的第2互连层。金属图案化之后,线间的空隙或用电介质填充、或在局部形成气隙。

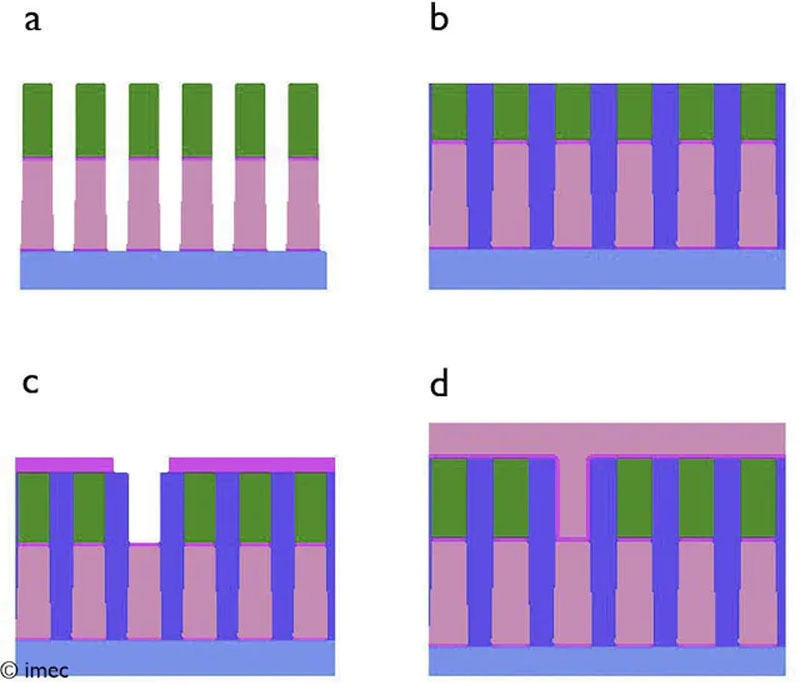

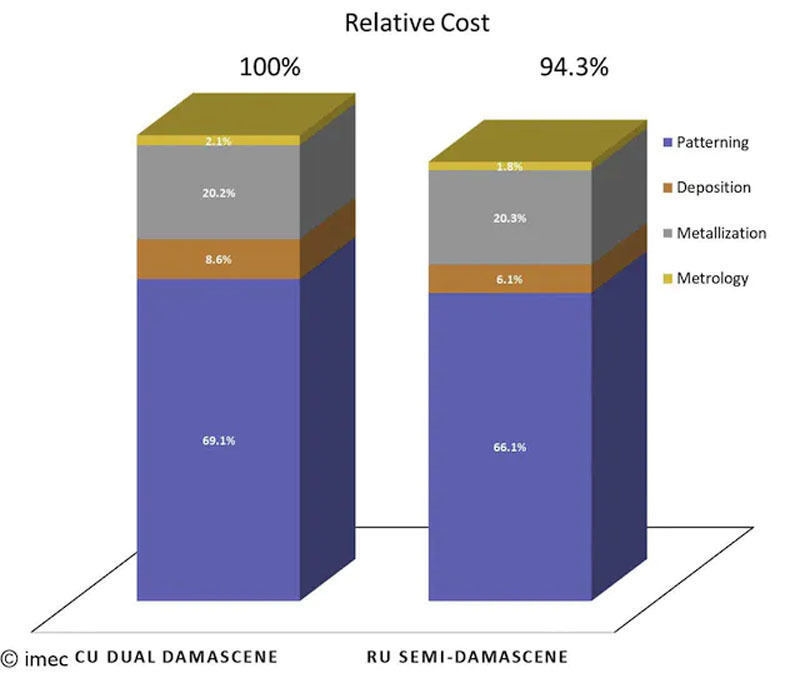

值得注意的是,半镶嵌工艺同样可以像以往的双镶嵌那样一次形成2个层(孔和顶部金属)。据此,通过和双镶嵌对照来看,半镶嵌可以有效地提高成本竞争力(参考图2)。

图2:18nm金属间距的Cu双镶嵌(左)和Ru半镶嵌(右)的成本比较。

半镶嵌工艺流程的优点

半镶嵌,在狭小金属间距方面相较于Cu双镶嵌有几个优点。imec的纳米互连项目总监Zsolt Tokei如下表示:

“半镶嵌,首先可以适用于更大的长宽比,因此易于控制电容,在防止RC延迟方面有优势。第二就是不用对金属进行CMP工序,因而工序方案更精简,效费比更高。最后就是半镶嵌不同于Cu那样需要钨(W)、钼(Mo)、钌(Ru)等无阻挡层且可图案化的金属,它使用不需要阻挡层的金属,可以借由互连金属自身来实现宝贵的导电区域的完全利用。这就确保了在尺寸缩放的情况下的导孔电阻值具有竞争力。” 当然了,即便加上上述优势,这种替代方案要想被业界所接纳还需要解决很多问题。朝此迈出的第一步,就是此次2个金属层级的实际演示方案。在此之前,其优势只是在虚拟与模型上展示过。完全自对准的导孔——重要的构成部分

对于20nm的狭小金属间距工艺来说,细小线路上受控的导孔是半镶嵌沉积模块正常运作的关键。如果孔与线(孔的上部与下部)没有对应到合适的位置,导孔与接触到的线路之间有漏电的风险。这些漏电路径会因为小小的导孔的图案化而导致叠加误差过大这一结果。

imec的技术员及骨干研究员Gayle Murdoch下述说到: “这个里程碑式的重要成果,是通过imec的集成、光刻、蚀刻和清洗团队之间的密切合作实现的。借由imec的自我整体统筹方式,才成功地将叠加误差控制在最大5nm。”

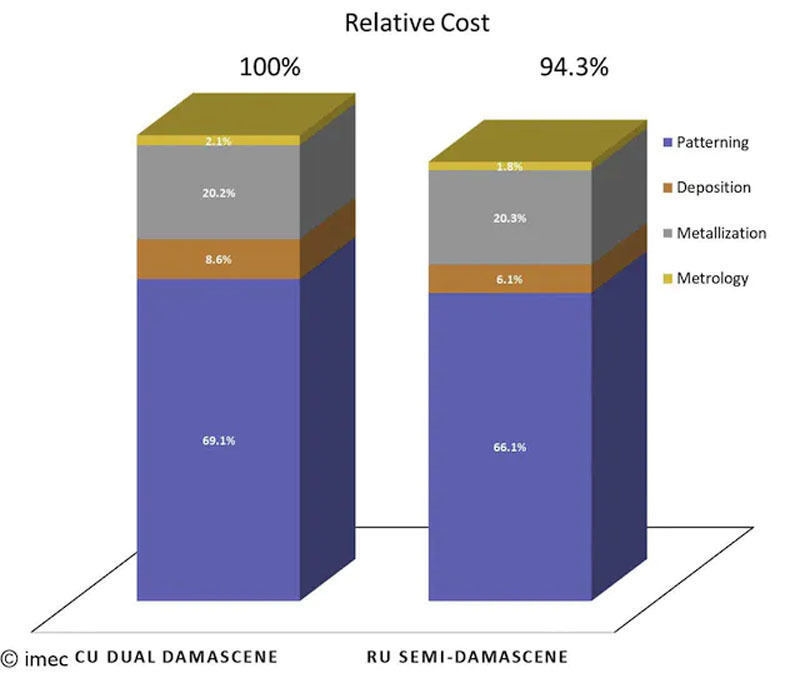

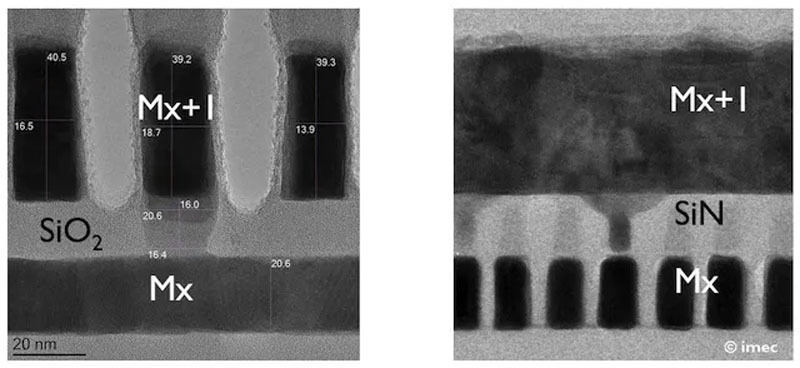

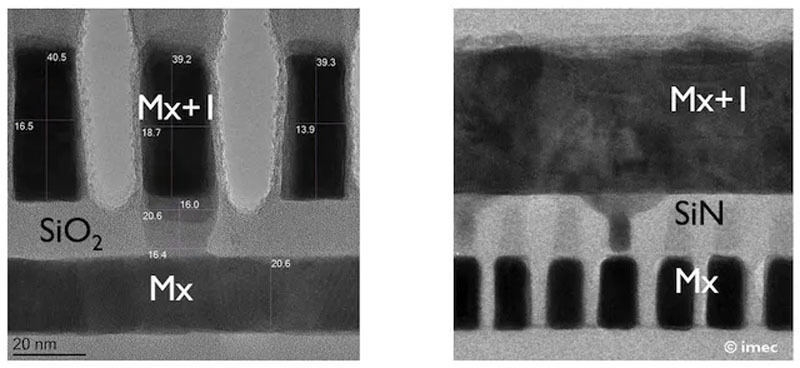

图3:Mx沿线(左)及Mx间(右)的自对准导孔。X-TEM表示的是18nm间距Ru线路上自对准孔的位置。

通过间隙填充后选择性地去除氮化硅保证了下方的自对准,在下方的金属线边缘上形成了导孔。与上方金属层(Ru)的自对准,是通过导孔过度填充和Ru图案化之后用到的Ru过刻蚀工序来实现的。

18nm间距中具有优越的耐受性和可靠性——首次演示

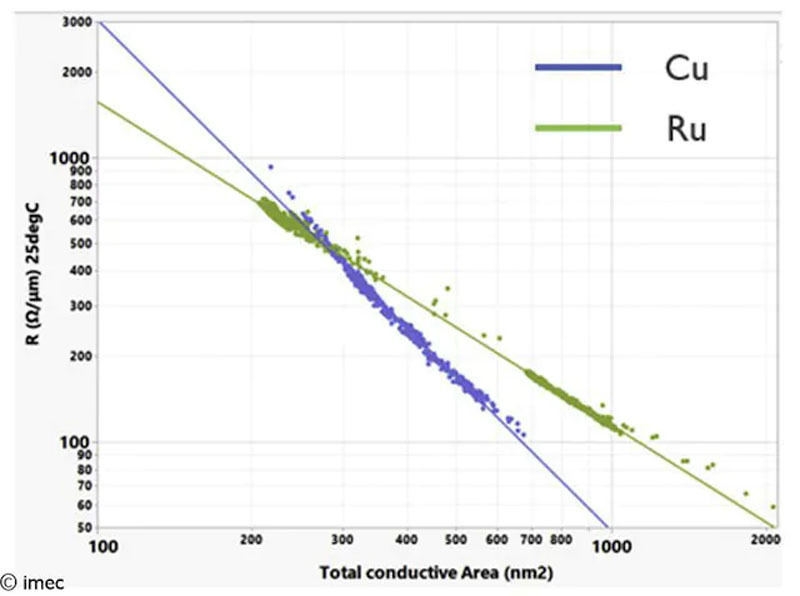

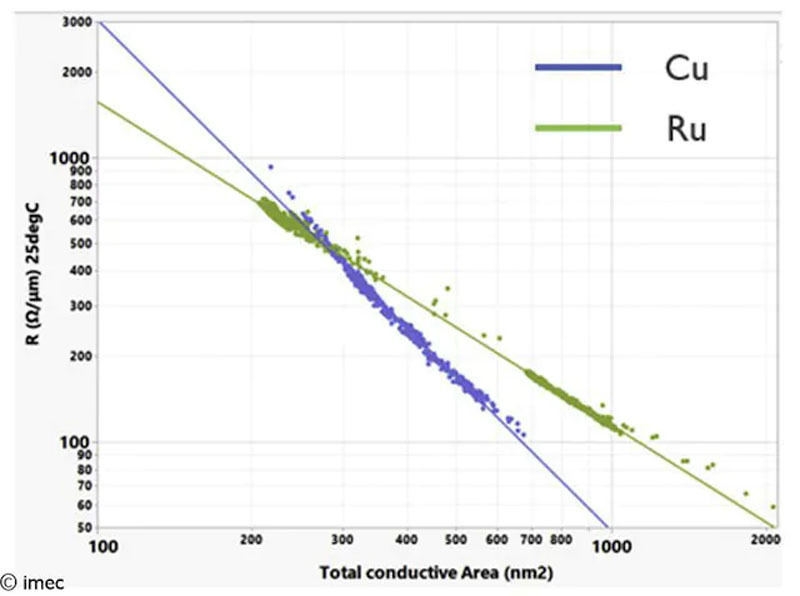

通过完全自对准的导孔,使用Ru的减法蚀刻,就得到了在18nm的金属间距下运作的2金属层级的元件。 把EUV光刻机与自对准双图案化(SADP)组合起来,将9nm的Ru下方局部互连线路(Mx)图案化,再使用单EUV光刻机形成上方线路(Mx+1)和导孔。 将Cu与Ru的布线电阻和导电面积进行对比,无论是从形态学上还是从电力学上都证实了Ru是理想的金属间层并且明显要优于Cu。达到了优异的导孔电阻(26~18nm的金属间距下,范围在40~60Ω)、证实了>9MV/cm 的孔到线的介质击穿电场。

图4:Ru及Cu线的导电面积和线路电阻的关系。

Zsolt Tokei表示:“导孔与线路的电阻值与可靠性等在内的所有重要技术参数方面,我们都得到了优异的数值。这意味着,1nm技术节点之后首次3个局部互连层堆积所需的双镶嵌技术,可以用半镶嵌工艺取代。imec的这个具备了完全自对准导孔的2金属层级器件证明了其重要的里程碑式的价值。”

如果在保留气隙(保证静电容量)的同时,加大线路的长宽比(减少电阻),该技术还有更大的改进空间。imec把继续推进中间工序(MOL)及使用半镶嵌技术(能够在标准单元层面上进一步减少面积的技术)的BEOL技术作为了今后的研究方向。